|

Zero i.e 8 bit data has been send to the receiver then PISO will send all This serial data is shifted in the SIPO of the comparator and this is the sipoop.EET 3350 Digital Systems Design Textbook: John Wakerly Chapter 8: 8.5 Shift Registers 1In my programme i have to Design a Serial In, Parallel Out, (SIPO) sift register with a Clock and Data input (both single lines and an 8-bit parallel output Q. Demonstrate one bit of storage capacity, and in a register, as. D flip-flop serial in/parallel out (DFF SIPO) based shift register. Following is VHDL code for an 8-bit shift-left register with a positive-edge clock, asynchronous parallel load, serial in, and serial out.74HC595 Serial-In-Parallel-Out shift register 74HC165 Parallel-In-Serial-Out shift register 74HC 194 4-bit bidirectional universal shift register In these ICs, mostly used are. IC 74674 16-bit parallel-in serial-out shift register with three-state outputs. Shift-registerIC 74673 16-bit serial-in serial-out shift register with output storage registers. A register is a digital circuit with two basic functions: Data Storage and Data Movement – A shift register provides the data movement function – A shift register “shifts” its output once every clock cycle.-serial input sout: out stdlogic -serial output ) end SReg architecture behavioral of SReg is signal tempreg: stdlogicvector(n-1.

The logic circuit diagram below shows a generalized serial-in serial-out shift register – SR Flip-Flops are shown – Connected to behave as D Flip-Flops – Input values moved to outputs of each Flip-Flop with the clock (shift) pulse N 1 0 N-Bit Shift Register 8 Asynchronous preset and clear inputs are used to set initial values 7 Movement can be left or right, but is usually only in a single direction in a given register One Flip-Flop for each bit to be handled The logic circuit diagram below shows a generalized serial-in serial-out shift register – SR Flip-Flops are shown – Connected to behave as D Flip-Flops – Input values moved to outputs of each Flip-Flop with the clock (shift) pulse N 1 0 N-Bit Shift Register 8 Asynchronous preset and clear inputs are used to set initial values 7 Movement can be left or right, but is usually only in a single direction in a given register One Flip-Flop for each bit to be handled

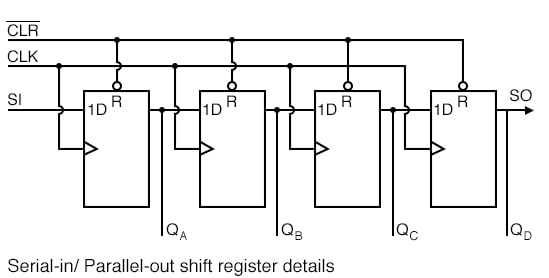

A simple way of looking at the serial shifting operation, with a focus on 1 the data bits, is illustrated at right 2 The Serial output (SO) is taken from the output of the rightmost Flip-Flop. The Serial input (SI) determines what goes into the leftmost Flip- Flop during the shift. Each clock pulse shifts the contents of the register one bit position to the right. The output of a given Flip-Flop is connected to the D input of the Flip-Flop at its right. This diagram shows the 4-bit sequence “1010” as it is unloaded from the 4- bit serial-in serial-out shift register Four clock pulses loads the register 11 Each bit moves one position to the right each time the clock’s leading edge occurs The diagram at right shows the 4-bit sequence “1010” being loaded into the 4-bit serial-in serial- out shift register Data is shown entering at left and shifting right 5 10 8 Bit Parallel In Serial Out Shift Register Vhdl Code Series Transmission SerialThe diagrams at the right illustrate a 4-bit serial-in parallel-out shift register We often need to convert from serial to parallel n-bit shift register – e.g., after receiving a series transmission Serial-in, serial-out shift registers are often used for data communications – such as RS-232 – modem transmission and reception – Ethernet links – SONET – etc. The upper shift register would “grab” the data once it was shifted into the lower register 16 These two shift registers are used to convert serial data to parallel data It would require N clock pulses to LOAD and one clock pulse to UNLOAD 15 We would use a serial-in parallel-out shift register of arbitrary length N to convert an N-bit word from serial to parallel Happy friday game download for macLogic circuit for a parallel-in, serial-out shift register 0 1 0 1 0 1Mux-like 18 It is then read out sequentially from the register one bit at a time from PA to PD on each clock cycle in a serial format The DATA is applied in parallel form to the parallel input pins PA to PD of the register

74LS164 logic diagram A LOW level on the Master Reset (MR) input overrides all other inputs and clears the register asynchronously, forcing all Q outputs LOW. 74LS164 is an 8-Bit Serial- In Parallel-Out Shift Register Parallel shift register (can serve as converting parallel-in to serial-out shifter): 22 Parallel-in, parallel-out shift register 0 1 0 1 0 1Mux-like 21 Each LOW-to-HIGH transition on the Clock (CP) input shifts data one place to the right Data is entered serially through one of two inputs (A or B) – either of these inputs can be used as an active HIGH Enable for data entry through the other input – an unused input must be tied HIGH, or both inputs connected together 26 The 74LS164 is an edge- triggered 8-bit shift register with serial data entry and an output from each of the eight stages. B) that existed before the rising clock edge.

0 Comments

Leave a Reply. |

AuthorDavid ArchivesCategories |

RSS Feed

RSS Feed